# PROTEUS DESIGN SUITE

**Getting Started Guide.**

## **COPYRIGHT NOTICE**

## © Labcenter Electronics Ltd 1990-2017. All Rights Reserved.

The PROTEUS software programs (ISIS Capture, PROSPICE Simulation and ARES Layout) and their associated library files, data files and documentation are copyright © Labcenter Electronics Ltd. All rights reserved. You have bought a licence to use the software on one machine at any one time; you do not own the software. Unauthorized copying, lending, or redistribution of the software or documentation in any manner constitutes breach of copyright. Software piracy is theft.

PROSPICE incorporates source code from Berkeley SPICE3F5 which is copyright © Regents of Berkeley University. Manufacturer's SPICE models included with the software are copyright of their respective originators.

The Qt GUI Toolkit is copyright © 2012 Digia Plc and/or its subsidiary(-ies) and licensed under the LGPL version 2.1. Some icons are copyright © 2010 The Eclipse Foundation licensed under the Eclipse Public Licence version 1.0. Some executables are from binutils and are copyright © 2010 The GNU Project, licensed under the GPL 2.

## WARNING

You may make a single copy of the software for backup purposes. However, you are warned that the software contains an encrypted serialization system. Any given copy of the software is therefore traceable to the master disk supplied with your licence.

PROTEUS also contains special code that will prevent more than one copy using a particular licence key on a network at any given time. Therefore, you must purchase a licence key for each copy that you want to run simultaneously.

## DISCLAIMER

No warranties of any kind are made with respect to the contents of this software package, nor its fitness for any particular purpose. Neither Labcenter Electronics Ltd nor any of its employees or sub-contractors shall be liable for errors in the software, component libraries, simulator models or documentation, or for any direct, indirect or consequential damages or financial losses arising from the use of the package.

Users are particularly reminded that successful simulation of a design with the PROSPICE simulator does not prove conclusively that it will work when manufactured. It is always best to make a one off prototype before having large numbers of boards produced.

Manufacturers' SPICE models included with PROSPICE are supplied on an 'as-is' basis and neither Labcenter nor their originators make any warranty whatsoever as to their accuracy or functionality

## TABLE OF CONTENTS

| COPYRIGHT NOTICE 1                                          |

|-------------------------------------------------------------|

| © Labcenter Electronics Ltd 1990-2017. All Rights Reserved1 |

| WARNING 1                                                   |

| DISCLAIMER 1                                                |

| TABLE OF CONTENTS                                           |

| SCHEMATIC CAPTURE TUTORIAL 1                                |

| INTRODUCTION1                                               |

| Creating a New Project2                                     |

| Guided Tour6                                                |

| Zooming7                                                    |

| Panning                                                     |

| Visual Aids to Design9                                      |

| Keyboard Shortcuts9                                         |

| Display Options                                             |

| Design Overview                                             |

| General Description                                         |

| Circuit Description                                         |

| Basic Schematic Entry 14                                    |

| Selecting Parts from the Library14                          |

| Placing Objects on the Schematic                            |

| Wiring Up 23                                                |

| Power Connections 27                                        |

| Part Labels and Annotation                                  |

| Timesaving Techniques & Block Editing31                     |

| Multi-Sheet Designs and Connectivity                        |

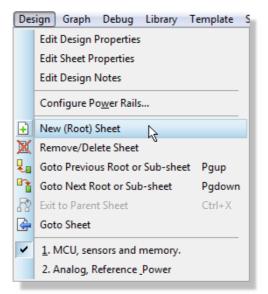

| Adding Sheets to a Design                                   |

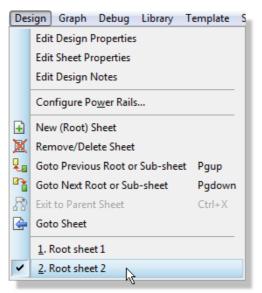

| Naming, Ordering and Navigating Sheets                      |

| Connectivity between Sheets 40                              |

| Gateswap                                                   |    |

|------------------------------------------------------------|----|

| Preparing for PCB Layout                                   | 44 |

| Packaging Considerations                                   | 44 |

| To view the package associated with a component:           |    |

| To change a package on a component                         |    |

| To change a package on all components of a particular type |    |

| Connectivity Considerations<br>To specify a new net class  |    |

| Design Verification                                        |    |

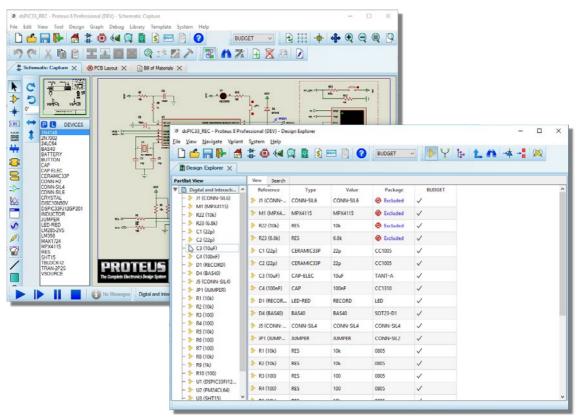

| The Design Explorer                                        |    |

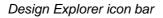

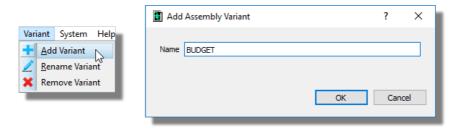

| Assembly Variants                                          |    |

| Bill of Materials                                          |    |

| Printing                                                   |    |

|                                                            |    |

| APPENDIX: Creating New Devices                             |    |

| Graphics and Pins                                          |    |

| Adding Footprints                                          |    |

| Adding Properties                                          |    |

| Attaching a Datasheet                                      |    |

| Indexing and Library Selection                             |    |

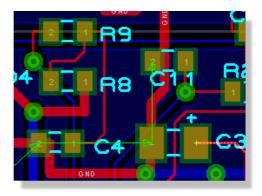

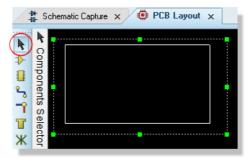

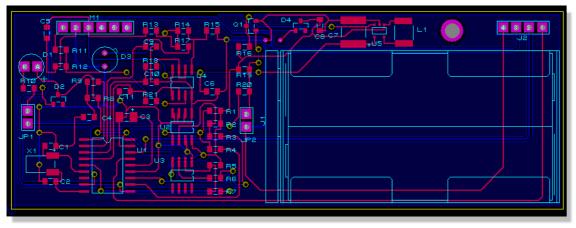

| PCB LAYOUT TUTORIAL                                        |    |

| Introduction                                               |    |

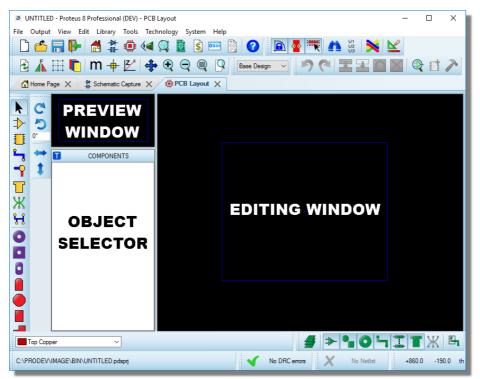

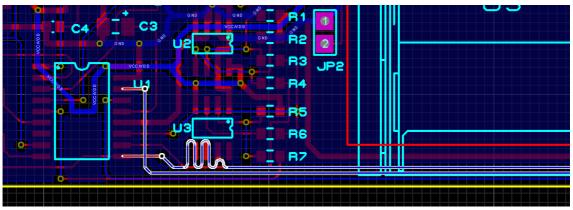

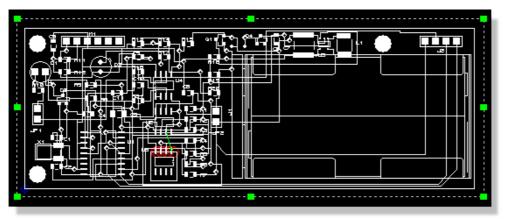

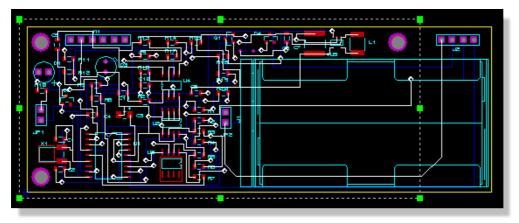

| Overview of the Layout Editor                              |    |

| The Main Window                                            |    |

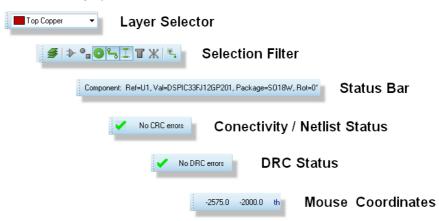

| The Control Bar                                            |    |

| Navigation                                                 |    |

| Visual Aids to Design                                      | 85 |

| Display Options                                            |    |

| Graphics Mode                                              |    |

| Opacity                                                    |    |

| Auto-Pan Animation                                         |    |

| Highlight Animation                                        | 87 |

| Multi-Sampling (Anti-Aliasing)                             |    |

| Displayed Layers Dialogue                                  |    |

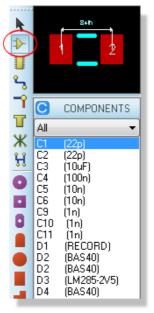

| Component Placement                      | . 90  |

|------------------------------------------|-------|

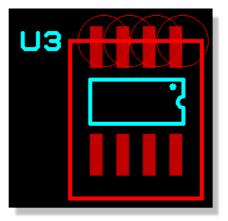

| Components and Packages                  | . 90  |

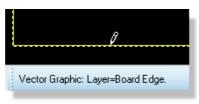

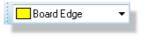

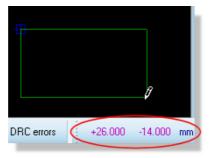

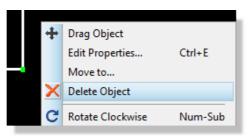

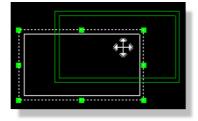

| The Board Edge                           | . 91  |

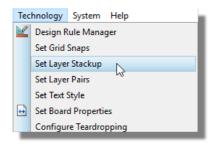

| Layer Stackup and Drill Spans            | . 94  |

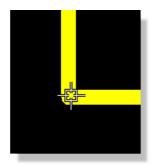

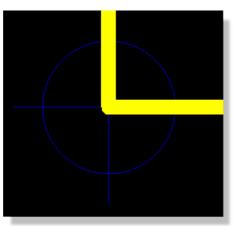

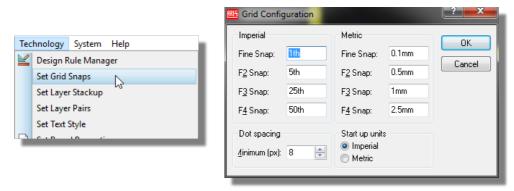

| Work Area, Co-ordinates and Snap         | . 96  |

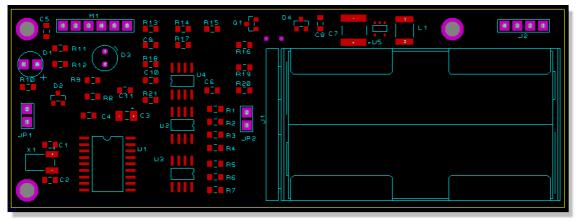

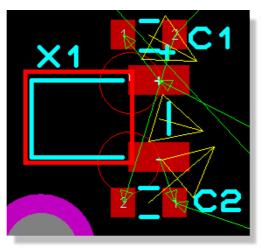

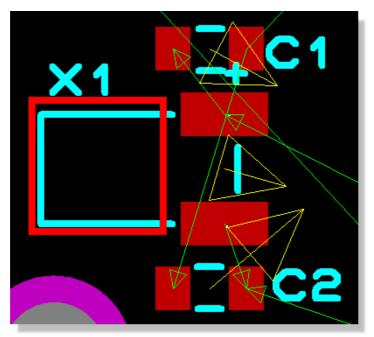

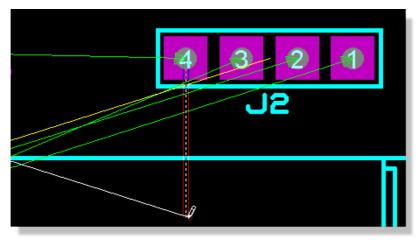

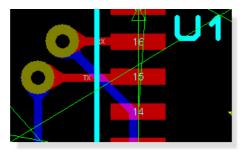

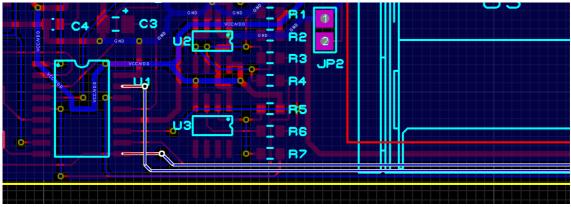

| Placing Components and the Ratsnest      | . 99  |

| Mounting Holes and Pad Styles            | . 106 |

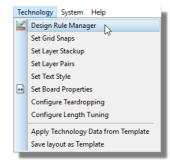

| Design Rules and Net Classes             | . 111 |

| Design Rules                             | . 112 |

| Net Classes                              | . 114 |

| Keepout Areas                            | . 117 |

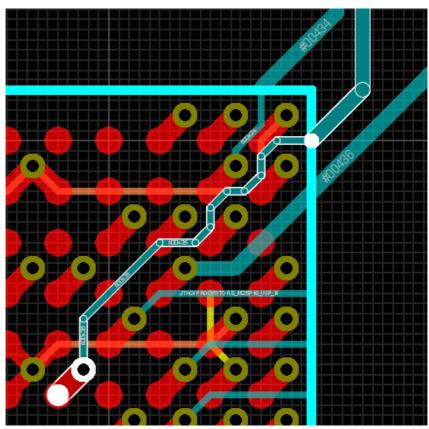

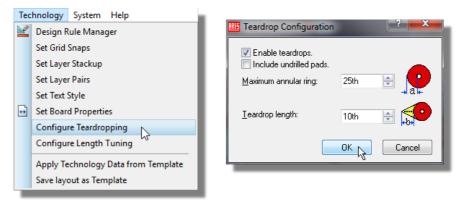

| Routing the Board                        | . 121 |

| Placing a Route Manually                 | . 122 |

| Panning and Zooming                      | . 126 |

| Placing Anchors                          |       |

| Getting Stuck / Re-routing while routing |       |

| Placing Vias                             |       |

| Object Hugging                           |       |

| Abandoning a Route                       |       |

| Making Connections                       |       |

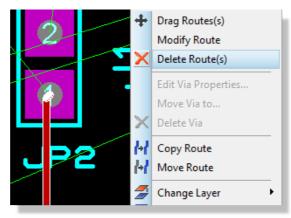

| Editing a Route                          |       |

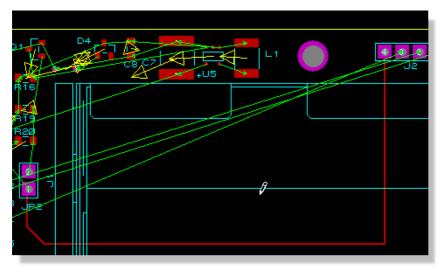

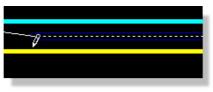

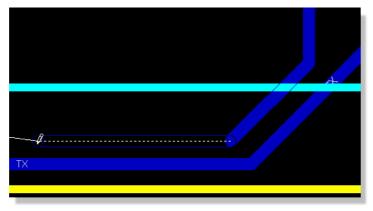

| Layer Pairs and Manual Routing           | . 130 |

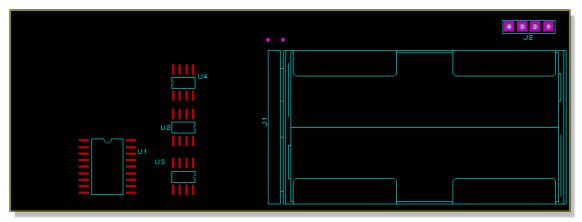

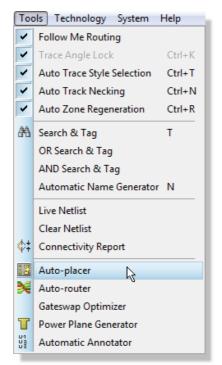

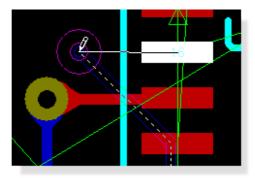

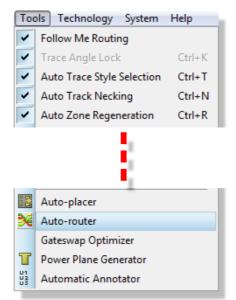

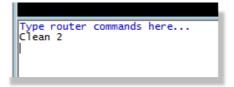

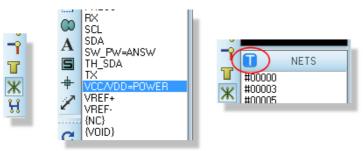

| Basic Auto-Routing                       | . 134 |

| Length Matching Routes                   | . 136 |

| The Selection Filter                     | . 138 |

| Advanced Auto-Routing                    | . 140 |

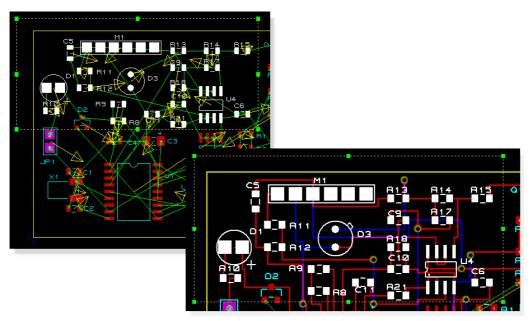

| Netlists and Design Changes              | . 144 |

| Live Netlisting                          | . 144 |

| Batch Netlisting                         | . 146 |

| Annotation                               | . 147 |

| Schematic to PCB                         | . 147 |

| PCB to Schematic                         | . 147 |

| General Netlisting Rules                 | . 148 |

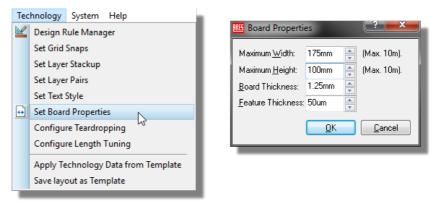

| Power Planes and Slots                | 148 |

|---------------------------------------|-----|

| Nesting and Islands                   | 151 |

| Relieve Pins                          |     |

| Exclude Tracking                      |     |

| Suppress Islands                      |     |

| Allow Nesting                         |     |

| Slots                                 |     |

| 3D Visualisation                      |     |

| Basic Navigation                      |     |

| Bareboard View and Height Clearances  |     |

| Custom Views                          |     |

| 3D Models (STEP/IGES)                 | 157 |

| Live Update                           | 158 |

| Board Output Options                  |     |

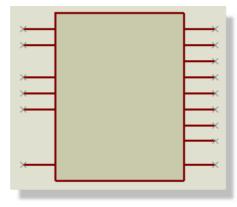

| APPENDIX: Creating New Packages       | 163 |

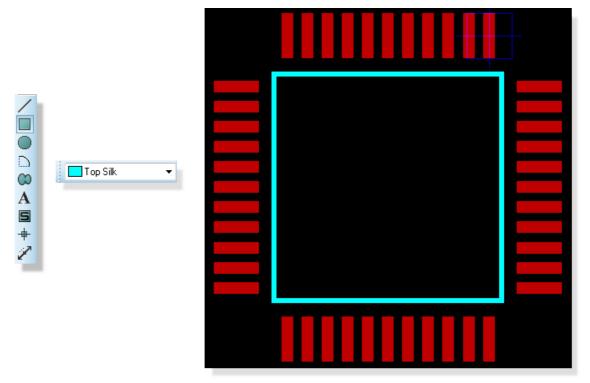

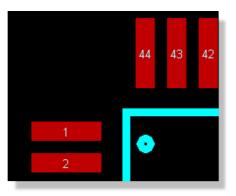

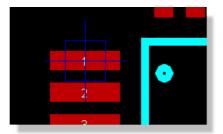

| Drawing the Footprint                 |     |

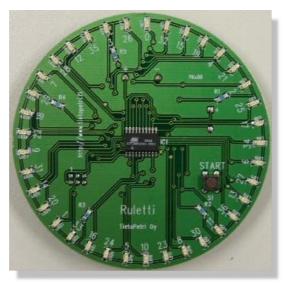

| Circular Pad Placement                |     |

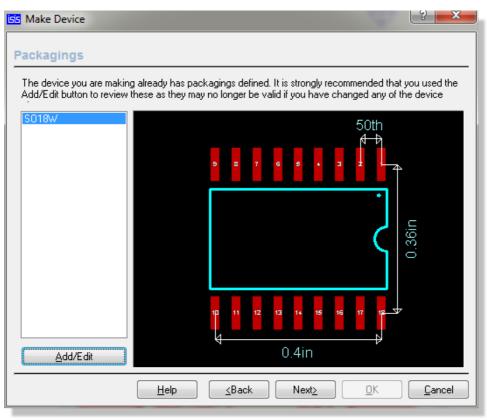

| Packaging the Footprint               | 174 |

| 3D Visualisation                      |     |

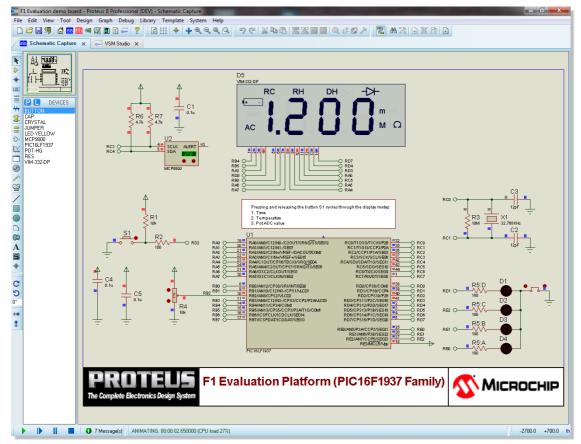

| VSM TUTORIAL (Interactive)            | 177 |

| Introduction – Interactive Simulation |     |

| Requirements                          | 178 |

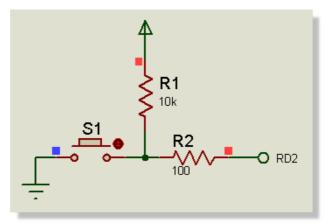

| Project Setup                         |     |

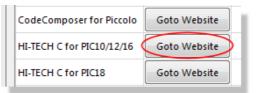

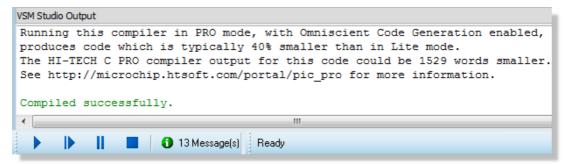

| Compiler Configuration                | 179 |

| Running a Simulation                  |     |

| Important Notes                       |     |

| Writing Firmware                      |     |

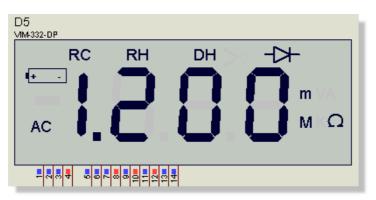

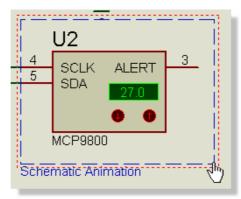

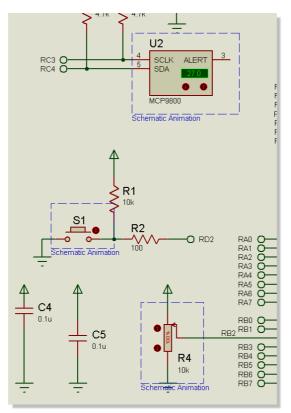

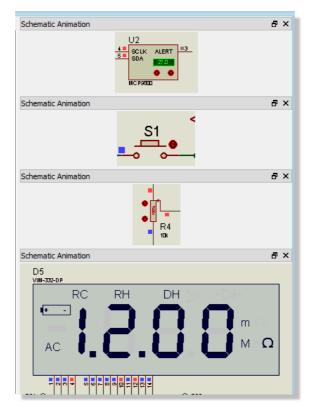

| Active Popups                         |     |

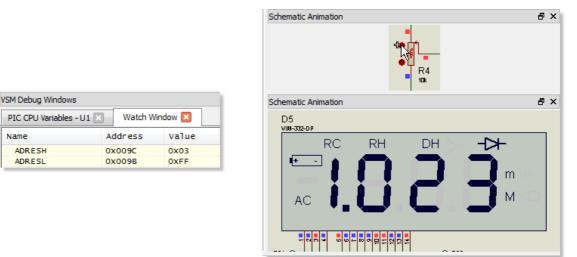

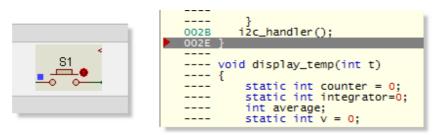

| Basic Debugging                       |     |

| Important Notes                       |     |

| The Watch Window                      |     |

| Hardware Breakpoints                  |     |

| Interactive Measurements              |     |

|   | Graph Based Measurements | . 205 |

|---|--------------------------|-------|

|   | Further Reading          | . 212 |

|   | Diagnostic Messaging     | 212   |

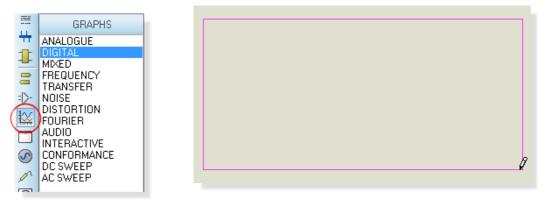

| V | SM TUTORIAL (Graphs)     | 217   |

|   | Getting Started          | 217   |

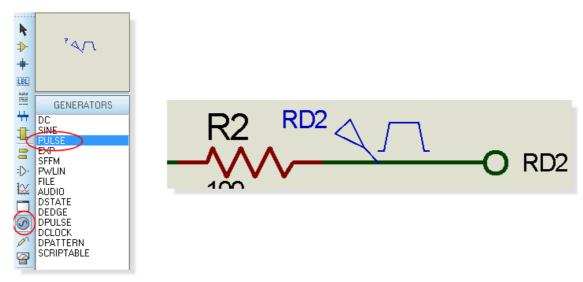

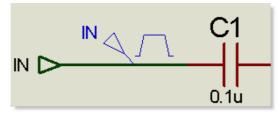

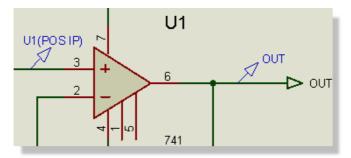

|   | Generators               | 218   |

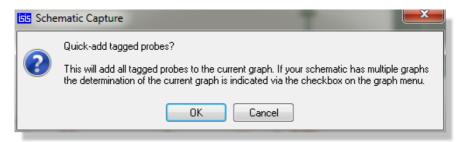

|   | Probes                   | 220   |

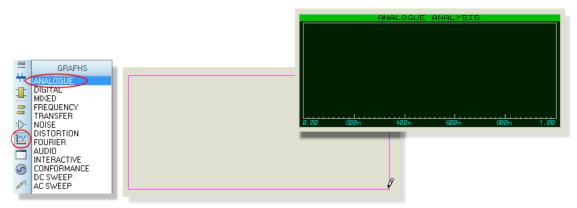

|   | Graphs                   | . 221 |

|   | Simulation               | 225   |

|   | Taking Measurements      | 226   |

|   | Using Current Probes     | 229   |

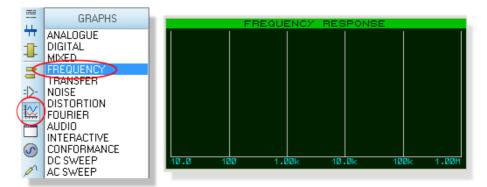

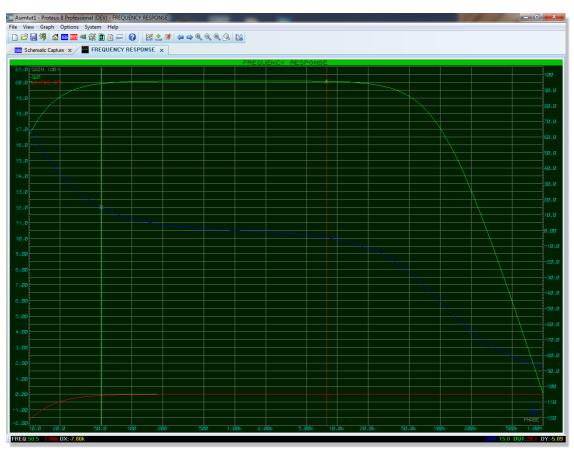

|   | Frequency Analysis       | . 230 |

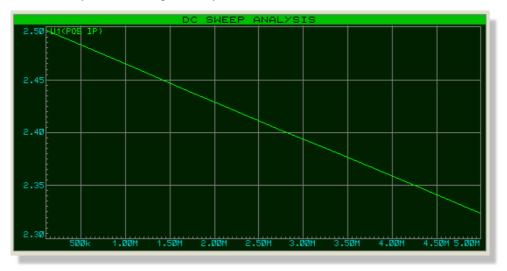

|   | Swept Variable Analysis  | 234   |

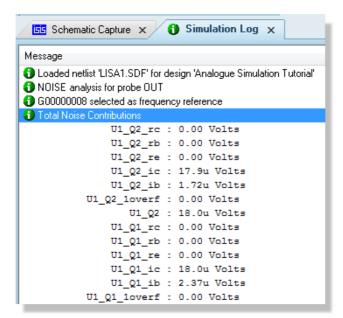

|   | Noise Analysis           | 236   |

|   |                          |       |

## SCHEMATIC CAPTURE TUTORIAL

## INTRODUCTION

The aim of this tutorial is to take you through the process of entering a circuit of modest complexity in order to familiarise you with the techniques required to drive the schematic capture module in Proteus (ISIS). The tutorial starts with the easiest topics such as placing and wiring up components, and then moves on to make use of the more sophisticated editing facilities, such as creating new library parts.

An accompanying tutorial in the PCB module (ARES) then continues the project development using the completed schematic drawn in this tutorial.

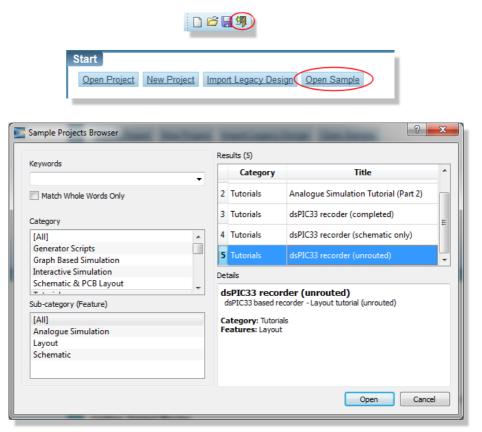

For those who want to see something quickly, DSPIC33\_REC\_SCHEMATIC.pdsprj contains the completed tutorial circuit but no layout while DSPIC33\_REC\_UNROUTED.pdsprj and DSPIC33\_REC\_COMPLETE.pdsprj both contain a completed schematic and a PCB. All of these projects can be loaded from the Open Sample command on the Proteus 8 home page under the tutorials category.

| Sample Projects Browser      |    | a line las        |                                       | ? <mark>X</mark> |

|------------------------------|----|-------------------|---------------------------------------|------------------|

| Keywords                     | Re | sults (5)         |                                       |                  |

| ×                            |    | Category          | Title                                 | <b>^</b>         |

| Match Whole Words Only       | 2  | Tutorials         | Analogue Simulation Tutorial (Part 2) |                  |

| Category                     | 3  | Tutorials         | dsPIC33 recoder (completed)           | =                |

| Interactive Simulation       | 4  | Tutorials         | dsPIC33 recorder (schematic only)     |                  |

| Schematic & PCB Layout       | 5  | Tutorials         | dsPIC33 recorder (unrouted)           | -                |

| Tutorials<br>VSM for 8051    |    |                   |                                       |                  |

| VSM for 8051<br>VSM for 8086 |    |                   |                                       |                  |

| Sub-category (Feature)       | A  | Analogue Simu     | llation Tutorial (Part1)              |                  |

| [AII]                        | с  | ategory: Tutorial | s                                     |                  |

| Analogue Simulation          | F  | eatures: Analogu  | ue Simulation                         |                  |

| Layout                       |    |                   |                                       |                  |

| Schematic                    |    |                   |                                       |                  |

|                              |    |                   |                                       |                  |

|                              |    |                   | Open                                  | Cancel           |

Note that throughout this tutorial (and the documentation as a whole) reference is made to keyboard shortcuts as a method of executing specific commands. The shortcuts specified are the default or system keyboard accelerators as provided when the software is shipped to you. Please be aware that if you have configured

your own keyboard accelerators the shortcuts mentioned may not be valid. Information on configuring your own keyboard shortcuts can be found in the General Concepts section of the Documentation.

#### **Creating a New Project**

We shall assume at this point that you have installed the Proteus 8 software package.

To start the software, click on the Start button and select Programs, Proteus 8 Professional and then the Proteus 8 application. The main application will then load and run and you will be presented with the Proteus home page.

If you have a Demonstration copy of the software you can start the Proteus application via the Proteus 8 Demonstration tab from the Start Menu.

In order to create a schematic we must first create a project. Since this tutorial is partnered with the PCB tutorial we will create a project for schematic/PCB.

Start by pressing the new project button near the top of the home page in Proteus.

| Start                                         |             |

|-----------------------------------------------|-------------|

| Open Project New Project Import Legacy Design | Open Sample |

On the first page of the wizard specify a name and path for the project.

| New F   | Project Wizard: Start                               | ? ×    |

|---------|-----------------------------------------------------|--------|

| Project | t Name                                              |        |

| Name    | MY_PROJECT.pdsprj                                   |        |

| Path    | D:\PROTEUS PROJECTS\                                | Browse |

| Ne      | ew Project 🔘 From Development Board 🔘 Blank Project |        |

We need a schematic so check the box at the top of the next step and then choose the default template.

|   | New Project Wizard: Schematic Design                | ? × |

|---|-----------------------------------------------------|-----|

|   | Create schematic design from the selected template: |     |

| L | Design Templates DEFAULT                            |     |

|   | Landscape A0                                        |     |

|   | Landscape A1                                        |     |

Similarly, we need a layout so check the box at the top of the layout page and again choose the default template.

| 2 | New Project Wizard: PCB Layout                | x |

|---|-----------------------------------------------|---|

|   | Create PCB layout from the selected template: |   |

|   | Layout Templates                              |   |

|   | DEFAULT                                       |   |

|   | Double Eurocard (2 Layer)                     |   |

|   | Double Eurocard (4 Layer)                     |   |

The next screen allows us to define the layer stack for our PCB. Since we will be designing a simple two layer board there is no configuration necessary here.

| 0 | New Pro           | oject Wizard: PCB L | ayer Stackup |                 |           |             |             |   | ?    | х |

|---|-------------------|---------------------|--------------|-----------------|-----------|-------------|-------------|---|------|---|

|   |                   |                     |              |                 |           |             |             |   |      |   |

|   | ID                | Name                | Туре         | Material        | Thickness | Dielectric  | Power Plane |   |      |   |

|   | TR                | Top Resist          | Surface      | Resist          | 10um      | 3.50        |             |   |      |   |

|   | TOP               | Top Copper          | Signal       | Copper          | 18um      |             |             |   |      |   |

|   |                   |                     | Core         | FR4             | 1.55mm    | 4.80        |             |   |      |   |

|   | BOT               | Bottom Copper       | Signal       | Copper          | 18um      |             |             |   |      |   |

|   | BR                | Bottom Resist       | Surface      | Resist          | 10um      | 3.50        |             |   |      |   |

|   |                   |                     |              |                 |           |             |             | _ |      |   |

|   | <                 |                     |              |                 |           |             |             | > |      |   |

|   | <u>S</u> tackup \ | Wizard Create P     | ower Plane   | Total Thickness | : 1.606mm | Slot Layer: | Mech 1      | ~ |      |   |

| 2 | Back              |                     |              |                 |           | Next        | Cancel      |   | Help |   |

• For multi-layer PCB's the stackup wizard button would be used to define the number of copper layers, cores and pre-preg's. This is discussed in more detail in the accompanying PCB tutorial.

The next screen is for configuration of drill spans. Again, for our proposed 2-layer board the only possibility is thru-hole so there is no action required.

| #<br>1 | Name<br>THRU | Start Layer<br>Top Copper | Stop Layer<br>Bottom Copper | Type<br>Through Hole |  |  |

|--------|--------------|---------------------------|-----------------------------|----------------------|--|--|

|        |              |                           | bottom coppor               | mough hole           |  |  |

|        |              |                           |                             |                      |  |  |

|        |              |                           |                             |                      |  |  |

| С      | reate from C | Cores Create from Via:    | s Add D                     | )elete               |  |  |

The final screen in the PCB configuration is simply a preview of a PCB cross section that displays visually what has been set up in the previous screens.

| New Project Wizard: PCB Board Preview | ?   | × |

|---------------------------------------|-----|---|

| Surface, 10um Resist                  |     |   |

| Core, 1.55mm FR4-                     |     |   |

| Surface, 10um Resist                  |     |   |

| Back Cancel                           | Hel | p |

We are not simulating the design so leave the firmware page blank and continue on to the summary which should look like the following:

| New Project Wizard: Summary                                                                                                                                                                                                                               |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Summary                                                                                                                                                                                                                                                   |  |

| Saving As: D:\Temp\New Project.pdsprj                                                                                                                                                                                                                     |  |

| ✓ Schematic                                                                                                                                                                                                                                               |  |

| Layout                                                                                                                                                                                                                                                    |  |

| Firmware                                                                                                                                                                                                                                                  |  |

| Details<br>Schematic template: C:\ProgramData\Labcenter Electronics\Proteus 8 Professional (DEV)\TEMPLATES\DEFAULT.DTF<br>Layout template: C:\ProgramData\Labcenter Electronics\Proteus 8 Professional (DEV)\TEMPLATES\DEFAULT.LTF<br>No Firmware Project |  |

|                                                                                                                                                                                                                                                           |  |

Click on the finish button to create the project.

- A schematic template can contain sheet size, colour scheme, company logo, header block and various other aesthetic presets. Further information can be found in the Templates chapter of the reference manual.

- A PCB template can contain board edge, mounting holes, design rules, layer stack and various other technology information. Refer to the Templates chapter in the PCB documentation for more information.

- The configuration of the Layer Stack and Drill Spans is really important for multi-layer PCB's and is discussed in some detail in the reference manual.

The project will open with two tabs, one schematic capture and the other for PCB layout. Click on the schematic tab to bring the ISIS module to the foreground.

## **Guided Tour**

The largest area of the screen is called the Editing Window, and it acts as a window on the drawing - this is where you will place and wire-up components. The smaller area at the top left of the screen is called the Overview Window. In normal use the Overview Window displays, as its name suggests, an overview of the entire drawing - the blue box shows the edge of the current sheet and the green box the area of the sheet currently displayed in the Editing Window. However, when a new object is selected from the Object Selector the Overview Window is used to preview the selected object - this is discussed later.

| New Project - Proteus 8 Profe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ssional (DEV) - Schematic Capture          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | n Graph Debug Library Template System Help |

| 0 😂 🔛 🗐 🚹 🚾 🕮 🖉                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                            |

| 90 XBG 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | a 🔯 🔍 🖈 🥻 🔭 🔁 🛤 🎉 🔂 🔀 🔀                    |

| Schematic Capture 🗙                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | CB Layout ×                                |

| R       C       Overview         ♥       0       Window         ₩        ●       Devices         ₩       ●       ●       Devices         ₩       ●       ●       Devices         ₩       ●       ●       ●         ●       ●       ●       ●         ●       ●       ●       ●         ●       ●       ●       ●         ●       ●       ●       ●         ●       ●       ●       ●         ●       ●       ●       ●         ●       ●       ●       ●         ●       ●       ●       ●         ●       ●       ●       ●         ●       ●       ●       ●         ●       ●       ●       ●         ●       ●       ●       ●         ●       ●       ●       ● <t< th=""><th>Editing Window</th></t<> | Editing Window                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | No Messages                                |

| Root sheet 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -18850.0 -150.0 th                         |

Isis Schematic Capture Window

If you don't like the default layout of the toolbars you can pick them up and dock them on any of the four sides of the application. Similarly you can move the Object Selector & Overview Window pane across to the right hand side of the application by dragging the end of it all the way across to the other side.

Toolbars and menu options will switch according to which tab is active (at the front). Throughout this tutorial when we refer to an icon or a menu command we are assuming that the schematic tab is active.

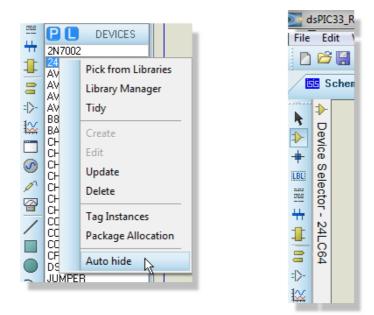

Right clicking the mouse either in the Object Selector or in the Overview Window will provide a context menu, including the option to 'auto hide' the left hand pane. This is extremely useful if you want to maximise the editing area of the application. When enabled the Object Selector and Overview Window will be minimised to a 'flyout bar' at the left (or right) of the application by default and will appear either when the mouse is placed over the bar or when the mode of operation is changed by selecting a different icon.

Auto hide the Object Selector

Device Mode Icon

Navigation of the view displayed in the Editing Window takes two forms; adjusting the scale of the drawing (zooming) and adjusting the area of the drawing displayed (panning). These techniques are somewhat intertwined and are discussed in more detail below:

## Zooming

There are several ways to zoom in and out of areas of the schematic:

- Point the mouse where you want to zoom in and out of and roll the middle mouse button (roll forwards to zoom in and backwards to zoom out).

- Point the mouse where you want to zoom in or out of and press the F6 or F7 keys respectively.

- Hold the SHIFT key down and drag out a box with the left mouse button around the area you want to zoom in to. We call this Shift Zoom

- Use the Zoom In, Zoom Out, Zoom All or Zoom Area icons on the toolbar.

Zoom Icons

- The F8 key can be used at any time to display the whole drawing.

- The Shift Zoom and the middle mouse zoom techniques can also be used over the Overview Window. That is, you can position the mouse over the Overview Window

and either roll the middle mouse button or use Shift Zoom to navigate in or out of an area of the schematic.

### Panning

As with zooming, there are a number of options for panning across the editing window.

- Click on the middle mouse button to enter track pan mode. This puts ISIS is a mode where the entire sheet is picked up and will move as you move the mouse. The track pan cursor will indicate when you have entered this mode. Left click the mouse again to exit track pan mode.

- To simply 'pan' the Editing Window up, down, left or right, position the mouse pointer over the desired part of the Editing Window and press the F5 key.

- Hold the SHIFT key down and bump the mouse against the edges of the Editing Window to pan up, down, left or right. We call this Shift Pan.

- Should you want to move the Editing Window to a completely different part of the drawing, the quickest method is to simply point at the centre of the new area on the Overview Window and click left.

- Use the Pan Icon on the toolbar

- Note that when using the track pan method above you can also zoom in and out by rolling the mouse wheel. So, click the middle mouse button to pick up the sheet and move the sheet by moving the mouse and zoom the sheet by rolling the middle mouse button. Left click to 'drop' the sheet and exit track pan mode.

It is well worth spending a few moments familiarising yourself with navigation in ISIS - it is after all one of the most common operations you will perform. In particular, learning to use the middle mouse button both for track pan and for zooming will save you time during schematic design.

A grid of dots or lines can be displayed in the Editing Window as a visual aid using the Grid command on the View menu, or by pressing 'G' to toggle the grid from 'dots', 'lines' or 'off, or by clicking the Grid Icon on the toolbar. The grid helps in lining up components and wires and is less intimidating than a blank screen. If you find it hard to see the grid dots or lines, either adjust the contrast on your monitor slightly (by default the grid is displayed in light grey) or change their colour with the Set Design Defaults on the Template menu.

Below the Overview Window is the Object Selector (sometimes known as a 'parts bin') which you use to select devices, symbols and other library objects. We'll familiarise ourselves further with using the Object Selector later.

Finally, at the bottom of the screen is the co-ordinate display, which reads out the co-ordinates of the mouse pointer when appropriate. These co-ordinates are in 1 thou units and the origin is in the centre of the drawing

Origin Co-ordinates

Note that ISIS allows you to reposition all the icon toolbars as well as move/resize the Object Selector/Overview Window. Do be aware however, that this documentation refers to all the rebars and windows in their default locations.

## **Visual Aids to Design**

ISIS is designed to be as user friendly as possible and provides two main ways to help you see what is happening during the design process – objects are encircled with a dashed line or 'twitched' when the mouse is over them and mouse cursors will change according to function. Essentially, the object-twitching scheme tells you which object the mouse is over (the 'hot' object) and the mouse cursor tells you what will happen when you left click the mouse on that object. While extremely intuitive, a summary of cursors used, together with their actions, is provided below:

| Cursor | Description                                                                                                                                         |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 2      | Standard Cursor - Used in selection mode when not over a 'hot' object.                                                                              |

| Ø      | Placement Cursor - Placement of an object will commence on a left click of the mouse.                                                               |

| 1      | Hot Placement Cursor - Appears green when placement of a wire is available on left click of the mouse.                                              |

| 1      | Bus Placement Cursor - Appears blue when placement of a BUS is available on left<br>click of the mouse.                                             |

| Spr)   | Selection Cursor - Object under the mouse will be selected on a left click of the mouse.                                                            |

| ~~~    | Move Cursor - The currently selected object can be moved.                                                                                           |

| 1      | Drag Cursor - The wire or 2D graphic can be dragged by holding the left mouse button down                                                           |

| ݱ      | Assignment Cursor - When over an object (having set the Property Assignment Tool)<br>You can assign the property by left clicking the mouse button. |

We will see more of the different cursor types throughout the course of the tutorial.

## **Keyboard Shortcuts**

For those customers who prefer to invoke commands and dialogues via the keyboard Proteus provides a comprehensive and flexible scheme for assigning shortcuts. The dialogue form is invoked from the System Menu – Set Keyboard Mapping command, where all commands and operation modes can be accessed from the combo box at the top. Simply select the command you want, apply a key sequence and assign it to that command

| 😼 Edit Keyboard Map                                                                                                                                                                                                                                                                                                     |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Command <u>G</u> roups:                                                                                                                                                                                                                                                                                                 |  |

| Schematic Window (File Menu) Commands                                                                                                                                                                                                                                                                                   |  |

| Available <u>C</u> ommands:                                                                                                                                                                                                                                                                                             |  |

| Import Legacy DSN file       Import Image         Import Section       Import Section         Export Section       Export Section         Export Bitmap       Export Bitmap         Export DXF File       Export DXF File         Export Adobe PDF File       Export Vector File         Print Design       Print Setup |  |

| Key sequence for selected command:                                                                                                                                                                                                                                                                                      |  |

| Options I                                                                                                                                                                                                                                                                                                               |  |

Keyboard Mapping Dialogue Form

While there are few limits on shortcuts, a few standard windows accelerators are restricted as they are global across the entire Proteus system (e.g. CTRL+S for save).

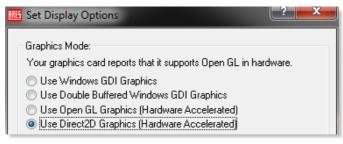

## **Display Options**

ISIS is capable of harnessing the power of your computers graphics card to speed up operation and present a crisp and smooth display. However, as not all machines have sufficient graphics cards the software is also capable of using Windows to perform display and graphical operations. The available modes of operation are called:

- Windows GDI Mode.

- OpenGL Hardware Accelerated Mode.

- Direct 2D Hardware Accelerated Mode.

If your graphics card is not powerful enough to support hardware acceleration then ISIS will simply default to Windows GDI mode. Should your computers graphics card be capable of both Direct2D and OpenGL the system will default to Direct2D mode as this tends to be more reliably implemented by graphics card vendors.

Configuration of the screen display takes place from the Set Display Options on the System menu. Some of these options are specific to a particular hardware acceleration technology and will be disabled when a different mode is enabled.

| Set Display Options                                                                                        |                                               |                                 | ? ×                          |

|------------------------------------------------------------------------------------------------------------|-----------------------------------------------|---------------------------------|------------------------------|

| Graphics Mode:<br>Your graphics card repo<br>Use Windows GDI G<br>Use Double Buffered<br>Use Open GL Graph | àraphics<br>1 Windows GDI<br>iics (Hardware A | Graphics<br>ccelerated)         | dware.                       |

| Auto-Pan Animation:<br>Pan Distance:<br>Number of Steps:<br>Pan Time (ms):                                 | 3                                             | 0                               |                              |

| Highlight Animation:<br>Animation Interval (ms):<br>Attack Rate:<br>Release Rate:                          | 100                                           | 0                               |                              |

| Multi-Sampling: 4x<br>N.B. Multi-sampling places                                                           | ▼<br>s significant dem                        | <u>D</u> K<br>ands on your grap | <u>C</u> ancel<br>hics card. |

The Set Display Options Form for OpenGL and Direct2D

The first section of the dialogue reports on whether your graphics card will support OpenGL and/or Direct2D hardware acceleration and, if so, allows you to switch between graphics mode.

The auto-pan section of the dialogue allows you to control distance, smoothness and speed of pan operations on the schematic. For example, holding down the shift key and bumping the mouse against the edge of the window will auto-pan the screen.

The highlight animation options allow you to specify the speed at which objects become active when the mouse is moved over them. The attack rate is the rate at which the object is highlighted and the release rate is the speed at which the object returns to its default state. These options are only available in hardware accelerated display modes.

Finally, the multi-sampling combo box allows you to specify the level of anti-aliasing you want when working in OpenGL mode. The higher the level of multi-sampling the better the antialiasing effect but the more GPU resources are consumed. If you select a level of multi-

sampling which is not supported by your graphics hardware the software will reset the level to the closest one which your card can handle.

- What you get with multi-sampling varies enormously between graphics cards. Some present extremely smooth text, while with others it looks blurry and on a few it causes display issues. We would suggest you being with multi-sampling off if you choose to work in OpenGL mode.

- Configuration of colours and styles in ISIS takes place from the Template Menu. This allows to change everything from paper, grid and highlight colours to the thickness and colour of all the object types used in a design. Please refer to the reference manual section on Templates for more information.

### **Design Overview**

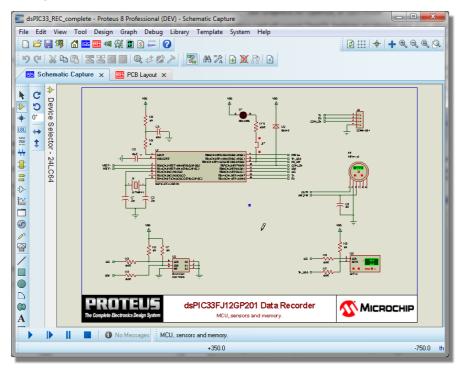

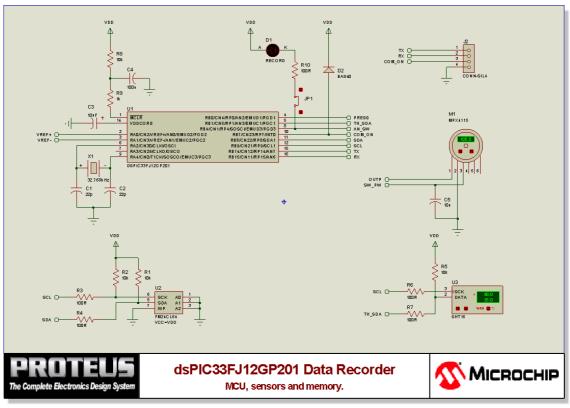

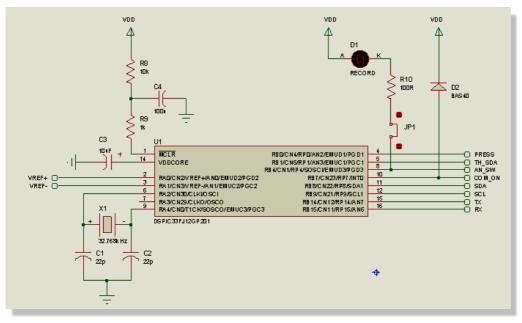

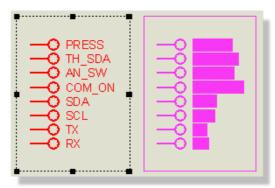

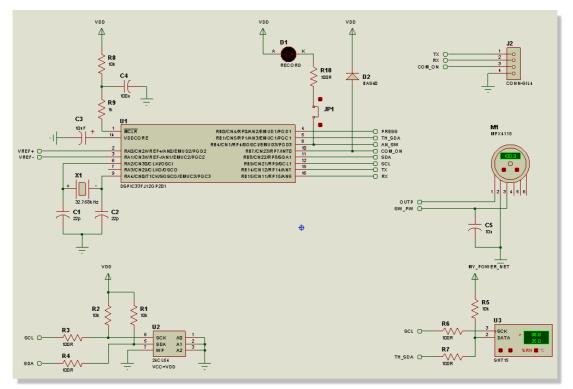

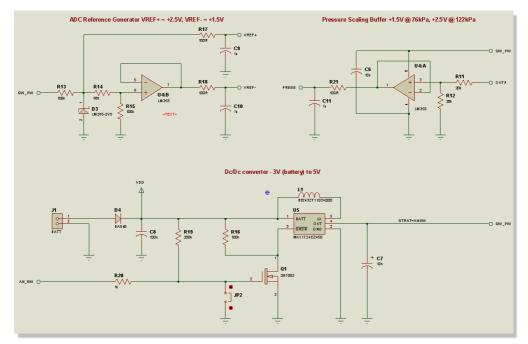

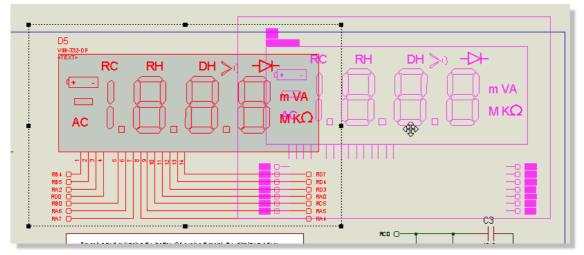

The circuit we are going to draw is shown below. This is reasonably straightforward schematic that will nonetheless allow us to cover most of the major features of the ISIS schematic capture package. Being a real-world design, it will also allow users to follow the design through the PCB phase of development via the PCB tutorial.

The dsPIC33 Data Recorder Sample Design

## **General Description**

The dsPIC33 Data Recorder Tutorial circuit is a solid state recorder designed to collect three of the most important environmental variables:

- Atmospheric pressure

- Ambient temperature

- Relative humidity

A number of low cost silicon transducers with built-in signal conditioning or digital interfaces have been used for measurement. This reduces the number of components to the minimum required for dsPIC33 interfacing.

All measurements get periodically stored into a non-volatile, low power memory in row binary format for later transfer to a host PC either by using a serial terminal or, more properly, a simple program (not supplied with the project). For the purpose of this project a serial terminal is used.

The circuit is designed to work with a battery for relatively long period in an unattended environment and, as such, a particular emphasis has been given to optimizing the power consumption and consequently the battery life. The recorder will sleep most of the time and will be woken up periodically only to accomplish the required recording operations.

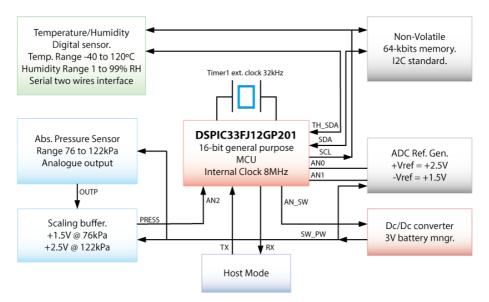

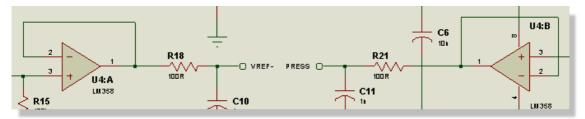

## **Circuit Description**

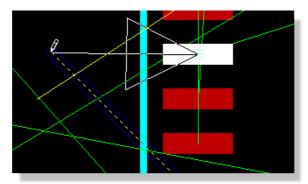

The following is a block diagram showing the behaviour and interaction of the circuit components.

Block diagram of the dsPIC Data Reorder Design

We'll cover the basics of the design construction as we progress through the tutorial but in order to keep the focus on the practical aspects of using the software, design decisions and theory will not be discussed in this document.

## **Basic Schematic Entry**

We'll start the tutorial by familiarizing ourselves with the basics of schematic design; picking components from the libraries, placing them on the schematic and wiring them together.

The design in question is relatively large and there is therefore a reasonable amount of drawing involved. We provide a completed schematic at the end of this section so, if you feel that you have mastered the basics at any point, there is no need to continue with drawing the remainder of the circuitry. We do however urge you to read through the full contents of the documentation as we introduce important features throughout.

The first thing we need to do is to get the parts from the libraries that we need in our schematic.

## **Selecting Parts from the Library**

You can select parts from the library in one of two ways:

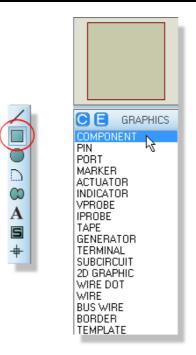

Click on the P button at the top left of the Object Selector as shown below. You can also use the Browse Library icon on the keyboard shortcut for this command (by default this is the P key on the keyboard).

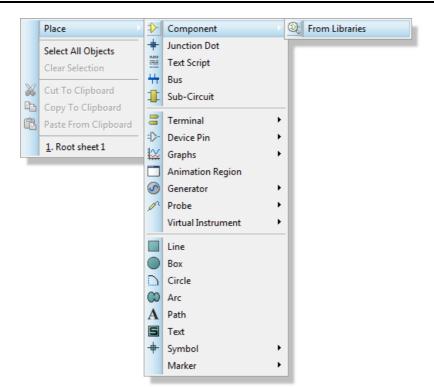

Right click the mouse on an empty area of the schematic and select Place – Component -From Libraries from the resulting context menu as shown below:

Either of these two methods will cause the Device Library Browser dialogue form to appear. For reference, the following is a list of all the components we will need for our design:

| 2N7002         | 24LC64          | AVX0805NPO22P    | AVX0805X7R1N | AVX08055X7R10N   |

|----------------|-----------------|------------------|--------------|------------------|

| AVX0805X7R100N | B82432T1103K000 | BAS40            | CHIPRES1K    | CHIPRES10K       |

| CHIPRES20K     | CHIPRES68K      | CHIPRES100K      | CHIPRES100R  | CHIPRES200K      |

| CONN-H2        | CONN-SIL4       | CONN-SIL6        | CRYSTAL      | DSPIC33FJ12GP201 |

| JUMPER         | LED-RED         | LM285-2V5        | LM358        | MAX1724          |

| MPX4115        | SHT15           | TAWD106M025R0600 |              |                  |

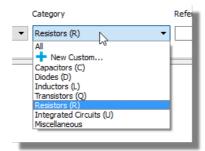

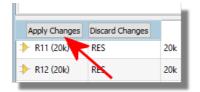

There are several ways in which we can find and import components from the libraries into the schematic. In the case of parts where you would know the part name it's usually best to start the search with that. Try entering '2N7002' into the Keywords field on the Device Library Browser dialogue form. This gives a direct result and we can then simply double click on the part in the results list to import it into the schematic. When you do this you should notice that the part now populates the Object Selector as in the following screenshot.

The 2N7002 in the Object Selector

Given that we know the names of all the parts we want we could simply proceed by using this technique to bring in all the components we need. However, this may not always be the case and ISIS provides several methods for finding parts in the component libraries. One of the most intuitive is to use the library browser a little like an internet search engine, typing in descriptive keywords and then browsing the results to find a specific part. Try this now with the resistors, typing in '1k resistor' in the keywords field of the library browser dialogue to locate the CHIPRES1K component (double click on the part in the results list to import into the schematic). We could similarly search for '10k SMT resistor' to find and insert the CHIPRES10k component and so on.

#### Schematic Capture

| Pick Devices                 |                          |           |                                                                                                                    | ? <mark>×</mark>             |

|------------------------------|--------------------------|-----------|--------------------------------------------------------------------------------------------------------------------|------------------------------|

| Keywor <u>d</u> s:           | <u>R</u> esults (10):    |           |                                                                                                                    | CHIPRES1K Preview:           |

| 1k SMT resistor              | Device                   | Library   | Description                                                                                                        | Analogue Primitive [RESISTOR |

| Match <u>W</u> hole Words?   | CHIPRES11K               | RESISTORS | 0.1W, 1%, 100ppm, SMT Thick film chip resistor (RL5000)                                                            |                              |

| how only parts with models?  | CHIPRES1K                | RESISTORS | 0.1W, 1%, 100ppm, SMT Thick film chip resistor (RL5000)                                                            |                              |

| ategory:                     | CHIPRES1K1               |           | 0.1W, 1%, 100ppm, SMT Thick film chip resistor (RL5000)                                                            |                              |

| All Categories)<br>Resistors | CHIPRES1K2               |           | 0.1W, 1%, 100ppm, SMT Thick film chip resistor (RL5000)                                                            |                              |

| realatora                    | CHIPRES1K3               |           | 0.1W, 1%, 100ppm, SMT Thick film chip resistor (RL5000)                                                            |                              |

|                              | CHIPRES1K5<br>CHIPRES1K6 |           | 0.1W, 1%, 100ppm, SMT Thick film chip resistor (RL5000)                                                            |                              |

|                              | CHIPRESTK6               |           | 0.1W, 1%, 100ppm, SMT Thick film chip resistor (RL5000)<br>0.1W, 1%, 100ppm, SMT Thick film chip resistor (RL5000) |                              |

|                              |                          |           | 0.1W, 1%, 100ppm, SMT Thick film chip resistor (RL5000)<br>0.1W, 1%, 100ppm, SMT Thick film chip resistor (RL5000) |                              |

|                              |                          |           | 0.1W, 1%, 100ppm, SMT Thick film chip resistor (RL5000)                                                            |                              |

|                              |                          |           |                                                                                                                    |                              |

|                              |                          |           |                                                                                                                    |                              |

|                              |                          |           |                                                                                                                    | PCB Preview:                 |

|                              |                          |           |                                                                                                                    |                              |

|                              |                          |           |                                                                                                                    |                              |

|                              |                          |           |                                                                                                                    | 4                            |

|                              |                          |           |                                                                                                                    |                              |

|                              |                          |           |                                                                                                                    |                              |

| ub-category:                 |                          |           |                                                                                                                    | 8                            |

|                              |                          |           |                                                                                                                    | 6                            |

|                              |                          |           |                                                                                                                    |                              |

|                              |                          |           |                                                                                                                    | 2                            |

|                              |                          |           |                                                                                                                    | <u> </u>                     |

|                              |                          |           |                                                                                                                    |                              |

| anufacturer:                 |                          |           |                                                                                                                    |                              |

| -                            |                          |           |                                                                                                                    | 0805 -                       |

|                              |                          |           |                                                                                                                    |                              |

|                              | •                        |           | • • • • • • • • • • • • • • • • • • •                                                                              | OK <u>C</u> ancel            |

Picking a CHIPRES1K Resistor from the Pick Devices form

• You can customize the information displayed in the Library Browser's results list by right clicking the mouse on the results list. The context menu provides you with options to display Categories, Sub-Categories, Manufacturer and Library alongside each result.

It may be that we simply want to browse for a specific type of part and/or one available from a specific manufacturer. To take an example, clear out the contents of the keyword field and then select the Capacitors Category. In our design we are looking for some Nickel Barrier caps from AVX so we can further filter the results set by selecting Nickel Barrier from the sub-category field and AVX from the Manufacturer field. There are still a large number of caps available so we might type in '22p', '1N', etc. in the keywords field to isolate and select the particular components we require (AVX0805NP022P, AVX0805X7R1N and so on).

Whilst this exercise is a little contrived given that we are starting from a preset list of parts, the techniques described are flexible enough to allow you to locate any library part quickly. Work through the full parts list for the design (as provided above) now using one or more of these

methods to find and select the parts into your design. When you are finished you should have all of the required components in the Object Selector as shown in the following screenshot.

| P DEVICES                |

|--------------------------|

| 2N7002                   |

| 24LC64                   |

| AVX0805NP022P            |

| AVX0805X7R1N             |

| AVX0805X7R10N            |

| AVX0805X7R100N           |

| B82432T1103K000<br>BAS40 |

| CHIPBES1K                |

| CHIPRES10K               |

| CHIPRES20K               |

| CHIPRES68K               |

| CHIPRES100K              |

| CHIPRES100R              |

| CHIPRES200K              |

| CONN-H2                  |

| CONN-SIL4                |

| CONN-SIL6                |

| CRYSTAL                  |

| DSPIC33FJ12GP201         |

| JUMPER<br>LED-BED        |

| LED-RED<br>LM285-2V5     |

| LM358                    |

| MAX1724EZK50             |

| MPX4115                  |

| SHT15                    |

| TAWD106M025R0600         |

A Full list of required components

For example, if you wanted to search for a specific stockcode you would need to make sure that the stockcode column was enabled (right click on results list) and then type something like 'digi <stockcode>' to locate the digikey stockcode.

Similarly, if you want to search through only your own library parts, you can simple enable the library field and then type something like 'user <partname>'; the user term will filter the results to the USERDVC library thus reducing the search range to your own libraries.

## **Placing Objects on the Schematic**

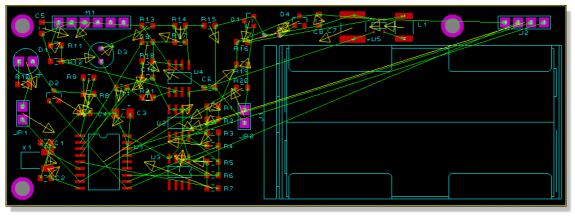

Having selected the parts we need the next thing is to actually place them on the drawing area – the Editing Window – and wire them together. You'll notice from the screenshot that we have also split the contents of the schematic into logical blocks of circuitry. This is partly aesthetic but also reduces wiring clutter on the schematic and will allow us to cover the use of terminals to form connections as we work through the tutorial.

Main Sheet of the dsPIC33 Data Recorder Schematic

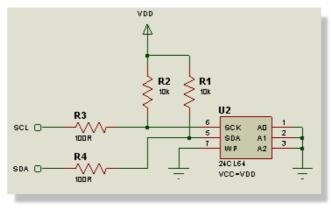

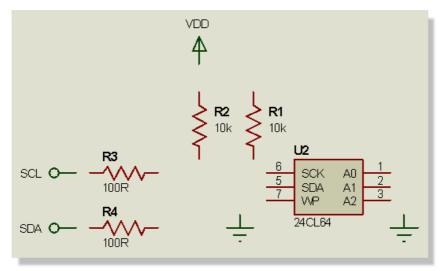

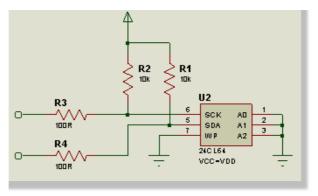

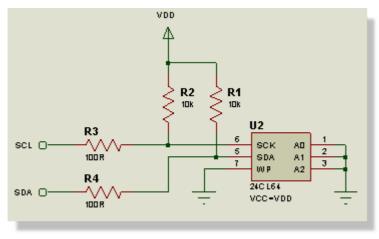

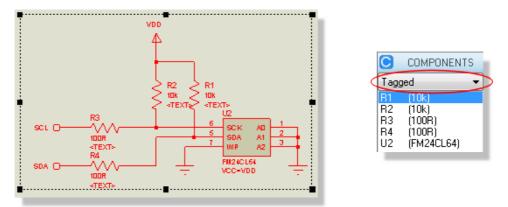

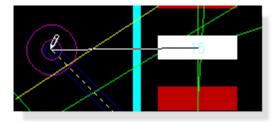

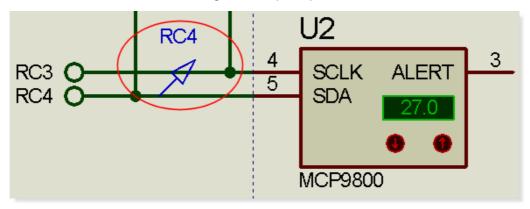

We are going to start off simply and complete the block of circuitry comprising the I2C Memory device as shown below.

I2C circuit section

Begin by placing the I2C memory device as follows:

Select the 24CL64 device from the Object Selector.

Left click on the schematic to enter placement mode.

Move the mouse to the desired location for the part, then left click the mouse again to 'drop' the part and commit placement.

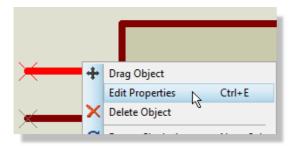

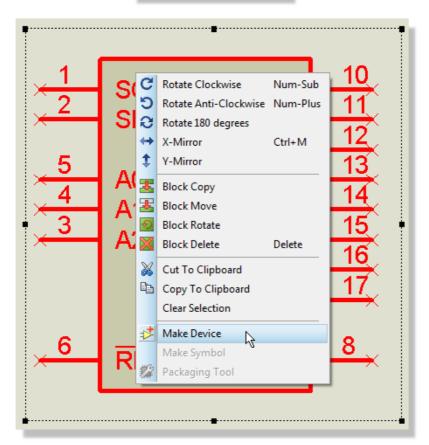

Often we need to move parts or blocks of circuitry after placement and now is a good time to cover the different ways in which we can do that. The procedure for this should be familiar to most users; we need to select the object(s) we want to move, left depress the mouse, drag to the new location and finally release the mouse to drop.

We can select an object in several ways as detailed below:

- Choose the Selection Icon and then left click on the object. This is a standard technique found in most graphical applications and will tag any object. Bear in mind when using this technique that you must change back to component mode for example, when you wish to perform other actions such as placing components etc.

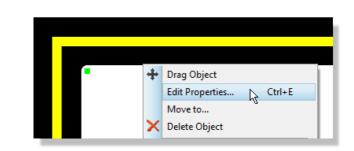

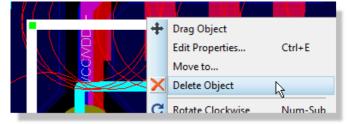

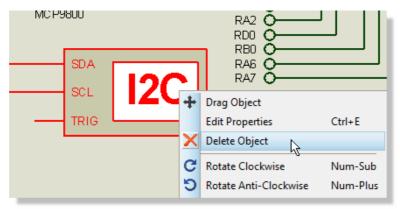

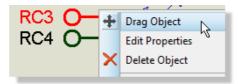

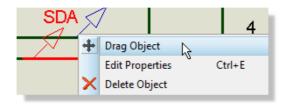

- Right clicking the mouse on an object will both tag the object and present a context menu containing available actions on that object.

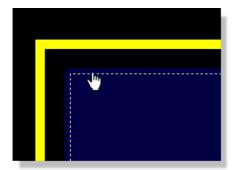

Draw a tagbox around the object by depressing the left mouse button and dragging the mouse to form a box encompassing the object to be selected. This method will work for any object (or indeed sets of objects). Sizing handles are provided to allow you to resize the tagbox in the event that it does not fully enclose the object. This is the technique that should be used for moving multiple, connected objects or blocks of circuitry.

We'll get plenty of practice moving things around as we lay out the schematic; for now just use one of these techniques to move the memory device down towards the bottom left of the Editing Window in roughly the same position as in the screenshot at the top of the section.

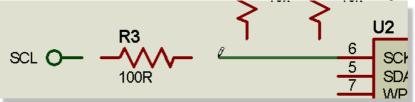

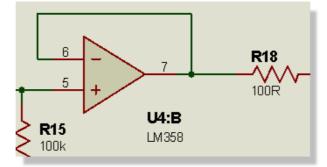

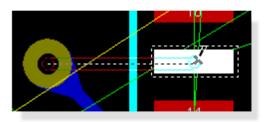

Having placed the memory device, we now need to get the peripheral circuitry down and oriented correctly. We are going to need two 10k pull up resistors and two 100 Ohm resistors for the data and clock lines. Additionally, we are going to need to use terminals to achieve connectivity with power, ground and other sections of circuitry. Begin by selecting the CHIPRES10k device and click left once on the anti-clockwise Rotation icon (shown below); note that the preview of the resistor in the Overview Window shows it rotated through 90°.

Using the Rotation Icons with the Overview window

Now place the resistor above and to the left of the memory device in the same way as before. Then, simply left click again on the Editing Window to start placing the second 10K resistor just beside the first one.

Next, select CHIPRES100R, rotate appropriately (see above) and place two to the left of the memory device in line with the SCK and SDA pins.

You can also rotate parts 'live' when in placement mode. Left click the mouse once to enter placement mode (at this point you will see the component outline following the mouse) and then use the '+' and '-' keys on the numeric keypad to rotate the component as you are placing it. Left click again to commit the placement in the normal way.

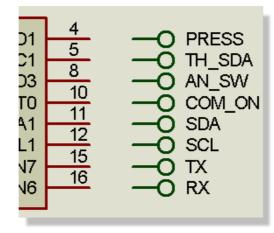

We use terminals in schematic design simply to terminate a wire and assign a connection. Often this connection is to either power or ground but it can just as easily be to another wire elsewhere on the circuit. Terminals allow us both to vastly reduce actual wiring (avoiding spaghetti schematics) and to make connections between different sheets on the schematic. To place terminals, start by selecting the terminal mode; this will switch the Object Selector and provide us with a listing of the available terminal types. We need a power terminal, ground terminal and also two default terminals for the connections on the I2C bus. From this stage, placement and orientation are identical to any other object in ISIS and should now be quite familiar. Place the appropriate terminals in their approximate locations now, such that the area around the memory device now looks something like the following

Selecting the Default Terminal

Unless you are fairly skillful, you are unlikely to have got all the components oriented and positioned entirely to your satisfaction at the first attempt, so now is a good time to practice moving things around as discussed earlier. In particular note that you can drag a tagbox around a group of objects to move the lot in one go.

Components positioned correctly

Similarly, you can clear a selection (or group of selections) either by left clicking in empty space or by right clicking in empty space and choosing the Clear Selection option from the resulting context menu

Dragging components

Remember that you can rotate while moving by using the '+' and '-' keys on the numeric keypad.

## Wiring Up

Having placed all the requisite components we now need to wire them together. There are three main techniques used to help make wiring a circuit as simple and quick as possible:

#### **Modeless Wiring**

There is no 'wiring mode' in ISIS - wires can be placed and edited at any time, without the hassle of entering a dedicated wiring mode prior to placement. This means less mouse travel, less mode switching and quicker development.

#### Follow-Me Wire Autorouting

After starting to place a wire, the proposed route of the wire will follow the movement of the mouse orthogonally to the termination point of the wire.

#### Live Cursor Display

The cursor will change as a visual indicator when wiring to show when a wire can be placed, when a wire can be terminated and when a wire is being placed.

The basic procedure for placing a wire between two pins is given below, using the connection between the SCK pin of the memory device and the 1000hm resistor as an example:

- Move the mouse over the SCK pin on the memory device the cursor will change to a green pen.

- Left click the mouse and then move it to the left until it is over the pin of the 100 Ohm resistor. The wire will follow the mouse and the cursor / pen is white during wiring

Left click the mouse again to commit the connection and place the wire.

The procedure for wiring onto an existing wire is almost identical but there are a couple of items to note:

- You cannot directly start a connection from an arbitrary point on a wire; in our example you want to start the connections from the pin and terminate them on the wire.

- When you terminate the connection on another wire a junction dot will be placed automatically to complete the connection.

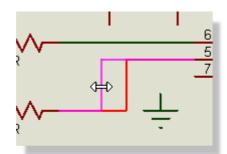

#### Dragging a wire

If, during a design, you want to make a wire-to-wire connection you must first place a junction dot on the wire and then wire from the junction dot to the other wire If you want to adjust a wire after placement (for example, the wire from the SDA pin to the resistor) then simply right click on the segment you want to move and then either select the 'Drag Wire' context menu option or simply depress the left mouse button and drag to the new location.

Armed with the above you should now be able to connect up all of the circuitry, so that your schematic now looks something like the following

Schematic section with all parts / terminals placed

• Remember, ISIS provides visual indicators to help you. If the cursor turns green you can start/stop wire placement.

#### **Connectivity by Touch**

The following basic rules of thumb may be helpful:

- If you are placing the component you can attach to another component, wire or terminal directly.

- If you are dragging the component you can attach to another component pin, junction dot or terminal.

- If you are copy and pasting you can only attach it to a pin end, a bus pin, a junction dot or a terminal only.

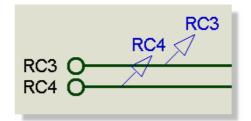

#### Making Connections with Terminals

The final thing we need to do to complete this block of circuitry is label the terminals. Terminal naming is extremely important as it denotes the connection to be made. We could name the terminals in any fashion we liked but sensible names make the schematic more legible and easy to understand.

Terminal connection

Power and Ground terminals are the exception to this rule, although there is no reason not to label them; an unlabeled power terminal is assigned to the VCC net and an unnamed ground terminal will be assigned to net GND.

Essentially what we are doing by labeling a terminal is making a connection to somewhere else on the schematic (a terminal with the same name) without placing a physical wire between the two objects.

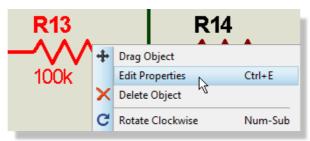

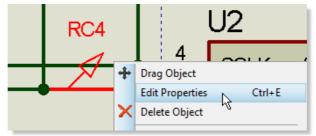

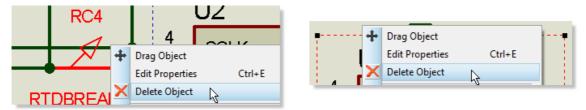

As discussed previously ISIS is flexible enough to present you with several methods for editing parts - choose your preferred method for editing the terminal from the following:

- Double left click on the terminal.

- Right click on the terminal to select it and launch the context menu and then use the Edit Properties menu option.

- Enter Selection Mode, left click to highlight the terminal, then right click to launch its context menu and use the Edit Properties menu option. Remember to exit selection mode when you are finished.

| isis Edit Termina | l Label        |          | ? ×        |

|-------------------|----------------|----------|------------|

| Label Style       |                |          |            |

| String:           | VDD            | •        | ▲uto-Sync? |

|                   | <u>R</u> otate | Vertical | Show All   |

Having now launched the terminals dialogue form, type in VDD in the edit field as shown below and hit ok to exit the dialogue form.

▲ Note that, where appropriate you should always prefix numerical terminal values with a '+' or '-'. For example, a terminal labelled 12V is ambiguous and you should therefore ensure it is labelled +12V or -12V.

Finish the job now by editing the other terminals and labeling them appropriately such that your completed circuit block now looks like the following:

Schematic section completed

## **Power Connections**

ISIS supports a powerful scheme for making power connections implicitly, thus vastly reducing the number of wires on the schematic. There are three main concepts involved that we will discuss in turn below.

#### **Hidden Power Pins**

Almost all relevant parts in ISIS have their power pins hidden (not visible on the schematic). The crucial point to remember is that in such cases is that by default the name of the pin denotes the net to which it will connect.

• For more information please visit Hidden Power Pins in the Online Help.

#### **Power Rail Configuration**

The easiest way to manage power nets and connectivity is through the Power Rail Configuration dialogue form, which is invoked from the Design Menu. If we do this now we can see that we have three pre-defined power supplies, namely GND, VCC/VDD and VEE. Changing the combo box at the top we should also see that the GND net is connected to the GND supply and that both the VCC and the VDD nets are connected to the VCC/VDD supply. It's worth examining how this happened more closely:

- The GND net is created by connections to an unlabeled ground terminal.

- The VDD net is created by connections to the power terminal labeled VDD.

- The I2C memory has two hidden power pins, VCC and GND, which are assigned to nets bearing their names.

Managing power nets and power supplies is a very important concept so we'll experiment a little to re-enforce the point. Exit the Power Rail Configuration dialogue form, right click on the I2C memory part and select Edit Properties from the resulting dialogue form. Next, click on the Hidden Pins button at the right hand side to view the hidden pins and their net assignments.

| Edit Component                                                                                                                                            | 0.5                                                                                                                                   | 8 X                                         |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|--|

| Part Value:<br>Element:<br>Data Write Time:<br>PCB Package:<br>Initial contents of memory:<br>Advanced Properties:<br>Log Start/Stop Conditions?<br>Pin I | U2<br>24CL64<br>In New<br>dit Hidden Power Pins<br>ar the name of the net a hidden pin st<br>nect to<br>GND: GND<br>VCC: VCC<br>OK Ca | Hidden: DK<br>Hidden: Hidden Pins<br>Cancel |  |

| Exclude from Simulation<br>Exclude from PCB Layout<br>Exclude from Bill of Materials                                                                      | Attach hierarchy module Hide common pins Edit all properties as text                                                                  |                                             |  |

Hidden Power pins in ISIS components.

Let's change the power pin to be on net VDD, instead of the default of VCC. If we then exit the dialog and re-invoke the Power Rail Configuration dialogue and switch to the VDD/VCC power supply we should see that the VCC net is no longer present (this was the only connection on our schematic so far).

While we are here and for completeness change the Voltage of the power supply to be 3.3V, which is actually what we will be using. In PCB Design this is useful only as a reference to ourselves but actually has significance in the software for simulation purposes. This exercise, while useful in explaining how to view/change the power nets for individual components, had no effect on design connectivity. The software is clever enough to assign both the VCC and the VDD nets to the same supply and the Power Rail Configuration dialogue allows us to configure our power connectivity at design level.

Returning to the schematic now, edit the VDD terminal (right click, edit properties) and change the terminal label to 'MY\_POWER\_NET'. If you go back to the Power Rail Configuration dialogue you should see that this is now an unconnected power net (a power net which is not associated with a power supply).

| Edit Terminal | Label                                                   | ? ×        |

|---------------|---------------------------------------------------------|------------|

| Label Style   |                                                         |            |

| String:       | MY_POWER_NET   Rotate  Horizontal  Vertical             | Auto-Sync? |

|               | Justify<br>◉Left ◯Centre ◯Right<br>◯Top ◉Middle ◯Bottom |            |

Changing the Terminal name

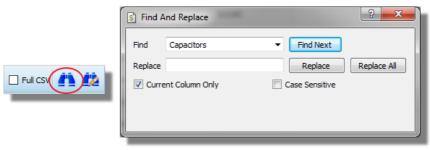

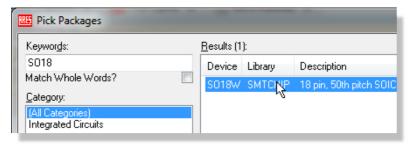

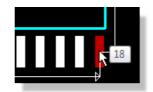

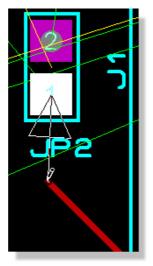

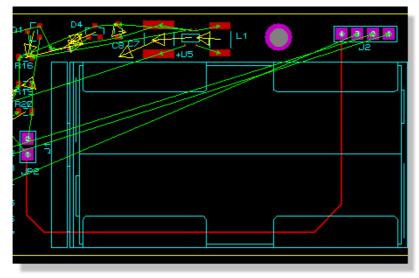

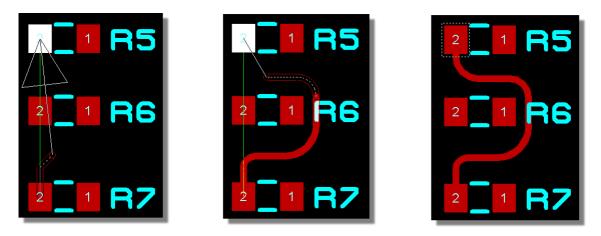

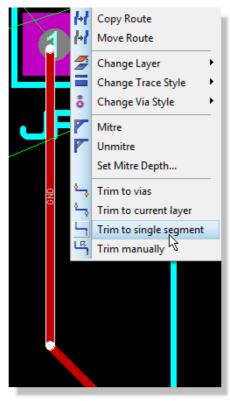

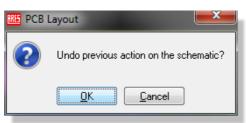

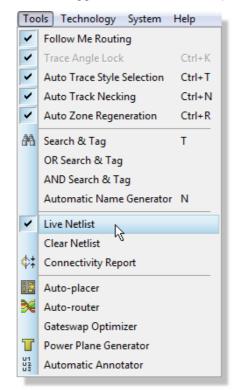

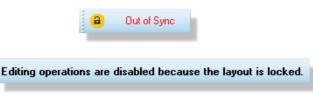

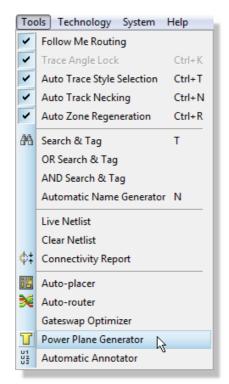

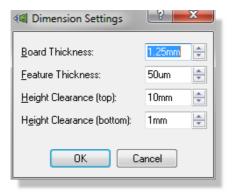

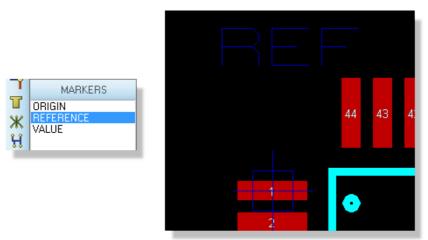

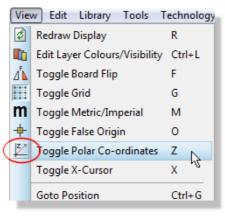

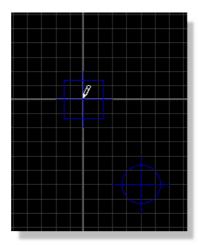

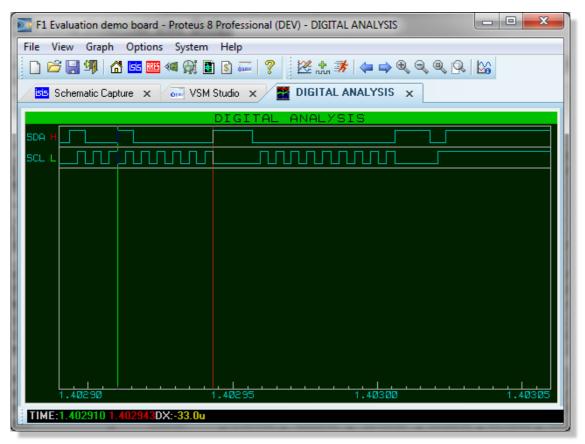

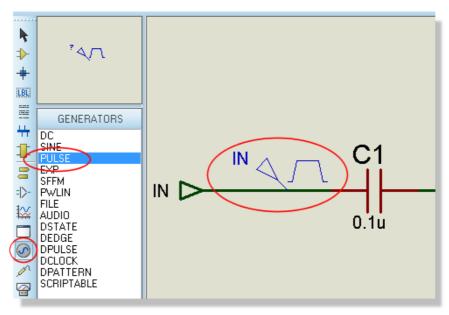

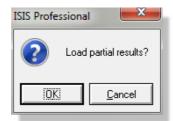

If we were doing this for real, we would now have to select the VSS/VDD power supply and then click the assign button to map our power net onto the correct supply.